쌓고 이어붙이고..미래 반도체 경쟁력 '포장'에 달렸다 [임주형의 테크토크]

성능 한 단계 끌어올릴 새 돌파구로 주목

애플 새 컴퓨터칩, 패키징 통해 진일보

다른 반도체 기업들도 잇따라 패키징 기술 공개

삼성, TSMC, 인텔 등 패키징 고객 유치 경쟁 치열

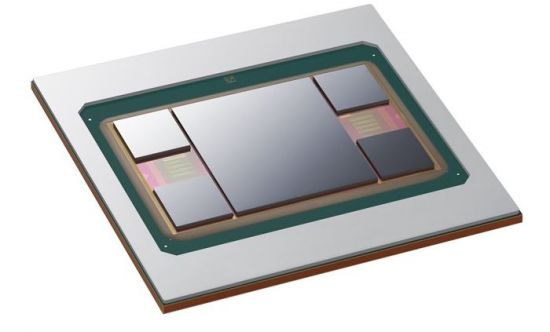

[아시아경제 임주형 기자] 머리카락 한 가닥 굵기보다 10만배 더 작은 나노미터(nm) 단위의 초미세공정을 필요로 하는 반도체. 반도체는 미세공정의 극치로 알려졌지만, 사실 반도체를 완성하려면 '포장' 작업도 중요합니다. 흔히 패키징이라고 불리는 후(後)공정으로, 반도체 내부의 회로가 훼손되지 않게 케이스를 씌우고 전기선을 외부로 연결하는 작업입니다. 하지만 마무리 작업이라고 해서 패키징을 간단한 기술로 얕봐선 안 됩니다. 최근 반도체 미세공정 기술이 한계에 봉착한 가운데, 패키징은 컴퓨터칩의 성능을 한 단계 진일보시켜 줄 새로운 활로로 여겨지고 있기 때문입니다.

◆글로벌 반도체 공룡들, 패키징 경쟁 점입가경

최근 국내 최대 기업인 삼성전의 사업 보고서에 따르면, 삼성 DS 부문 글로벌 제조&인프라 총괄 내에 '테스트&패키지(TP) 센터'가 신설됐습니다. TP센터는 반도체 제조에 필요한 설비와 환경, 인프라 조성을 관리하는 한편 패키징 기술 개발을 주력으로 하는 부서입니다.

삼성은 반도체 설계 기업으로부터 도면을 받아 직접 생산을 하는 '파운드리' 사업부를 가진 기업입니다. 이번 패키징 부서 강화는 미래 패키징 기술을 미리 확보하고, 다른 파운드리 기업들과의 경쟁에서 유리한 고지를 차지하기 위함인 것으로 보입니다.

패키징 기술 개발에 박차를 가한 것은 삼성뿐만이 아닙니다. 인텔은 지난해 미국 뉴멕시코주에 35억달러(약 4조2700억원)를 투자해 반도체 패키징 시설을 새로 구축했고, 올해 하반기부터 가동을 시작할 예정입니다.

세계 1위의 파운드리 기업인 TSMC는 지난해 패키징 공정에만 무려 150억달러(약 18조3100억원)를 쏟아부었습니다. 미 금융 매체 '블룸버그'에 따르면, TSMC는 패키징 기술의 전통적 강자인 일본 기업들과 밀접한 협력 관계를 맺을 예정입니다.

◆애플 M1 울트라, 울트라퓨전 패키징으로 성능 극대화

패키징은 만들어진 반도체에 케이스를 씌우고 전기선을 연결하는 후공정 작업입니다. 실제 반도체의 공정과는 크게 관련 없으므로, 컴퓨터칩의 성능과 동떨어진 중요도가 떨어지는 작업이라고 생각하기 쉽습니다.

하지만 최근 반도체 기업들은 컴퓨터칩의 성능을 한 단계 끌어올릴 수단으로 패키징을 주목하고 있습니다. 반도체 위에 새로운 칩을 올려 '3D화'하는 작업, 혹은 반도체 옆에 또 다른 반도체를 이어붙여 전체 성능을 강화하는 작업 등이 패키징 덕분에 가능해졌기 때문입니다.

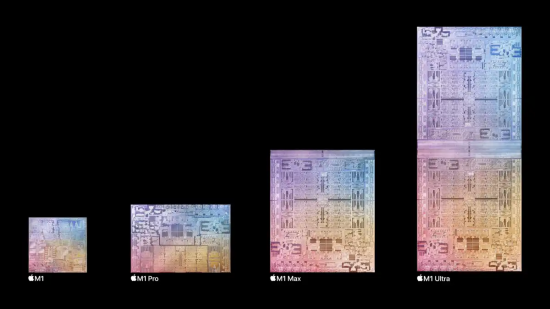

패키징을 통해 반도체의 성능을 개량한 대표적인 사례로는 애플의 새로운 시스템-온-칩(SoC)인 'M1 울트라'가 있습니다. 지난 9일(현지시간) 공개된 M1 울트라는 애플의 신형 컴퓨터에 탑재될 예정인데, 크기는 물론 성능도 역대 최대인 칩입니다.

애플은 어떻게 이런 칩을 만들 수 있었을까요. M1 울트라를 다른 M1 칩들과 비교해 보면 그 비결을 알 수 있습니다. M1 울트라는 이전 세대 제품인 M1 맥스의 딱 두 배 크기인데, 왜냐하면 M1 맥스 두 개를 서로 이어붙인 칩이기 때문입니다. 이 연결 방식은 애플이 '울트라퓨전'이라고 칭하는 패키징 기술로 완성한 겁니다.

칩과 칩을 서로 이어 하나의 SoC로 만든다는 것은 결코 말처럼 쉬운 일이 아닙니다. 소프트웨어가 칩을 하나로 인식할 수 있도록, 전력, 발열량, 초당 대역폭 등 미세한 부분을 하나하나 신경 써서 공정해야 하기 때문입니다.

하지만 이런 방식을 구현하는 데 성공하기만 하면 기업 입장에선 막대한 이득을 누릴 수 있습니다. 우선 새 칩을 처음부터 끝까지 다시 만들 필요가 없으므로 연구 비용을 아낄 수 있고, 기존에 있던 칩을 계속 만들면 되기 때문에 생산도 용이합니다.

◆미세공정은 점차 한계 도달…패키징, 새 돌파구 될 수 있을까

칩과 칩을 연결하는 패키징 기술은 아직까지는 새로운 분야입니다. 현재까지 소수의 기업들만이 이런 공정으로 만든 칩을 내놓고 있습니다.

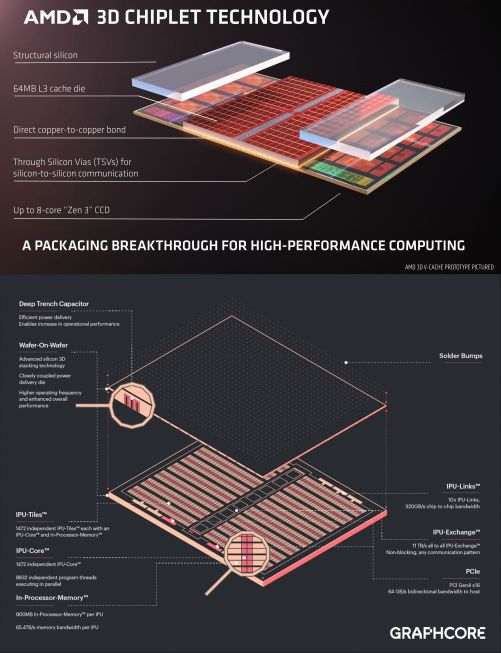

또 다른 패키징 사례로는 미국의 반도체 기업 'AMD'가 내놓은 '3D V-캐시'가 있습니다. 기존 CPU 반도체 기판 위에 V-캐시를 추가로 '쌓아 올려' 성능을 강화한 버전입니다.

그런가 하면 영국의 스타트업이자 인공지능(AI) 반도체 전문 설계 기업 '그래프코어'는 세계 최초로 기판 위에 또 다른 기판을 얹는 방식인 'Wafer on wafer(웨이퍼 온 웨이퍼·WoW) 패키지 공정을 성공해 업계의 주목을 받기도 했습니다.

그래프코어는 '지능처리유닛'이라는 AI 전용 칩을 설계하는데, 이 회사는 기존 2세대 칩 위에 전력 보급용 추가 기판을 얹어 패키징함으로써 성능을 40% 끌어올리고 전력 소비량은 16% 줄이는 쾌거를 이룩했다고 합니다.

기업들이 반도체 패키징에 열중하는 이유는 미세 공정의 한계 때문입니다. 현재 대부분의 최신 마이크로프로세서는 7nm 공정으로 만들고, 애플의 'M1' 시리즈 같은 최첨단 칩은 5nm 공정으로 만들어집니다. 삼성전자, TSMC 등은 3nm 칩 양산 기술을 실현하기 위해 막대한 자본을 투자하고 있습니다.

nm의 숫자가 줄어들수록 반도체 내 회로가 미세해지고, 더 많은 트랜지스터를 집적할 수 있다는 뜻이므로 성능이 높아집니다. 하지만 미세공정이 1nm에 근접하면서, 양산 난이도는 더욱 높아지고 비용도 기하급수적으로 커지고 있습니다. 또 반도체 공정이 1nm 수준에 근접할수록 트랜지스터는 거의 원자 크기까지 축소되는데, 원자 단위에선 회로 속에 흐르는 전자가 갑자기 다른 곳으로 순간이동하는 '양자 터널 효과'가 발생할 수 있어 효율성이 급격히 감소할 위험도 있습니다.

이렇다 보니 반도체 기업들은 패키징에서 돌파구를 찾는 겁니다. 기존에 있는 반도체 위에 또 다른 반도체를 쌓거나, 혹은 옆에 이어붙이는 것만으로도 만족할 만한 성능 증진을 이룰 수 있다면 '미세공정 경쟁'의 부담이 크게 줄어들기 때문입니다.

물론 패키징 공정은 결코 간단한 게 아닙니다. WoW 공정을 실현한 그래프코어의 경우, 칩 위에 또 다른 칩을 쌓는 '1단 쌓기' 공정을 완성하기 위해 TSMC와 1년6개월 가까이에 걸쳐 공동 연구를 했다고 합니다.

사이먼 놀스 그래프코어 최고기술자는 "우리는 WoW 공정을 완성하기 위해 지난 2020년부터 18개월 가까이 TSMC와 밀접하게 협력해 왔다"라며 "다른 기업들이 우리와 같은 방식으로 새 칩을 만들려면, 적어도 상당한 기간을 연구 개발에 투자해야만 할 것"이라고 지적했습니다.

즉, 복잡한 패키징 공정을 실현하려면 설계 기업과 생산 기업 공동의 노력이 필요하며, 그 과정에서 누적된 노하우는 다른 회사가 쉽게 베낄 수 없다는 뜻입니다. 삼성전자, TSMC, 인텔 등 반도체 생산 기업들이 패키징 시장 고객을 최대한 빨리 유치하기 위해 분투하는 이유입니다.

임주형 기자 skepped@asiae.co.kr

Copyright © 아시아경제. 무단전재 및 재배포 금지.

- "너무 하얘 장어인줄 알았어요"…제주 고깃집발 '나도 당했다' 확산 - 아시아경제

- 민희진 "풋옵션 30배 요구는 보이그룹 제작 반영한 것" - 아시아경제

- 저걸 왜 사나 했는데…기안84, 5년만에 '62억 건물주' 됐다 - 아시아경제

- 김흥국 "연락도 없다고 했더니 야단 맞았나…나경원·권영세 등 갑자기 연락" - 아시아경제

- '무자본 갭투자' 빌라·오피스텔 400채 매수…보증금 110억원 챙긴 전세사기 일당 검거 - 아시아경

- 단월드 "종교단체 아니다…BTS와 무관" 하이브 연관설 부인 - 아시아경제

- 차에 치인 강아지에 군복 덮어주고 마지막 지켜준 군인 - 아시아경제

- 여친 숨졌는데 "헤어졌다"고 말한 거제 폭행남 - 아시아경제

- ‘몸 좋고 맘 좋은 영양 산나물 축제’, 바가지 없는 착한가격 - 아시아경제

- 주차시비로 여성폭행한 전직 보디빌더측, 탄원서 75장 제출 '선처호소' - 아시아경제